## WDFN6 2x2 µCool<sup>™</sup> 506AP Single MOSFET Package Board Level Application Notes and Thermal Performance

#### Prepared by: Anthony M. Volpe ON Semiconductor Introduction

New ON Semiconductor  $\mu Cool^{TM}$  MOSFETs in a WDFN6 2x2 506AP package are thermally enhanced and remarkably small to exclusively address power management challenges in portable devices such as synchronous buck and boost circuits, high and low side load switches, and lithium–ion battery charging circuits.

This technical note discusses the single-channel WDFN6 506AP package overview, pad patterns, evaluation board layout and thermal performance.

#### **Package Overview**

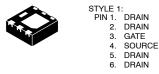

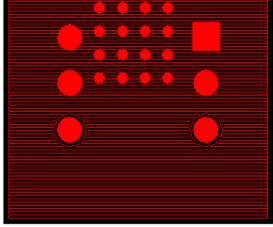

Figure 1 illustrates a single site WDFN6 semiconductor device package and pin-out description. A half etch lead-frame complements mold lock features allowing this leadless package to provide an exposed drain pad for excellent thermal conduction and reduced electrical parasitics. The low profile (< 0.8 mm) compact design is similar to the popular DFN/QFN package allowing for an easy fit in thin environments. Suggested guidelines for mounting criteria on a printed circuit board (PCB) are outlined in application note AND8211/D.

Figure 1. The Underside of a Single-Chip 6 Pin WDFN Package

#### **Basic Pad Pattnes**

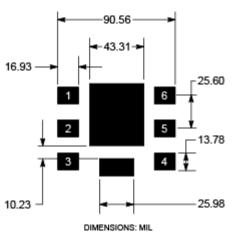

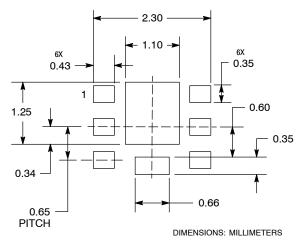

A recommended solder-mask defined mounting footprint is defined in Figure 2. The WDFN6 506AP footprint dimensions are the same as a standard SC-88 and SC-70-6 package. However, the underside of the 506AP package offers the added feature of an exposed flag acting as a drain contact and heat dissipation path to promote operation at a lower junction temperature.

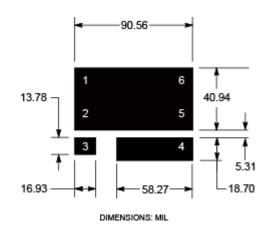

Figure 3 depicts a minimum recommended pad pattern that confines an improved thermal area of drain connections (Pins 1, 2, 5, 6) to the basic footprint. In addition, increasing

http://onsemi.com

## **APPLICATION NOTE**

the contact area of the exposed source to include Pin 4 promotes a decrease of inductance. A drain copper area of 2.39 sq. mm assists in directing the power dissipation path through the copper lead-frame and into the board. The addition of vias to other board layers further enhances device performance. An evaluation board containing the minimum recommended pad pattern and aforementioned vias is shown in Figure 4 of the subsequent section.

Figure 2. Basic Pad Layout

Figure 3. Minimum Recommended Pad Pattern

## **Evaluation Board**

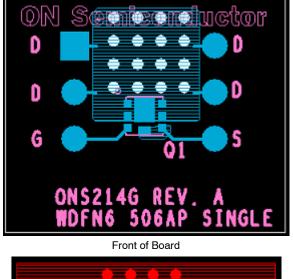

The evaluation board, shown in Figure 4, measures  $0.6 \times 0.5$  inch. The board contains 1 oz. copper thickness on top-side and 1 oz. copper thickness on the underside. Vias are added through to the underside of the board where contact is made with a copper pad area of approximately board size dimensions. On top-side, the copper pad area surrounding the four drain leads is increased to approximately 0.0544 square inch resulting in a total dissipation path area of 0.3544 square inch.

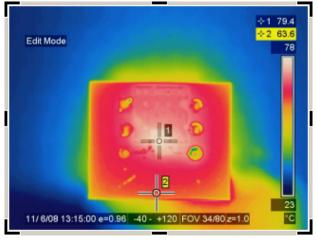

Back of Board Figure 4. Evaluation Board

This 6-pin DIP design allows the use of sockets and facilitates wire interfacing. Figure 5 represents a WDFN6 506AP package mounted on the evaluation board with and without test pins. A quick thermal analysis of this board is conducted by inducing a saturation current of 820 mA. This yields a junction temperature of  $79.4^{\circ}$ C and a board temperature of  $63.6^{\circ}$ C. Figure 6 shows a thermal image of this board under the aforementioned conditions.

Figure 5. Mounted Device

Figure 6. Thermal Image of Mounted Device

Further results from the measured thermal performance of this package are described in the subsequent section. Testing included a thermal analysis of the package surface mounted on a FR4 board using one-inch square pad size and the minimum recommended pad size.

## THERMAL PERFORMANCE

## **Assumptions and Definitions**

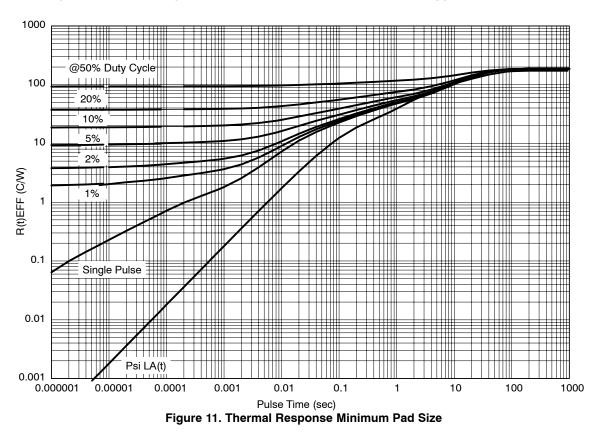

The subsequent sections outline the thermal performance of a WDFN6 506AP package. All values and equations are obtained from simulations and pertain to the Theta(DC) matrix unless otherwise specified. A 10% duty cycle is arbitrarily chosen to evaluate various thermal responses. Refer to Figure 11 for thermal responses at varying duty cycles. The simulation models used to derive the results in this section are modeled around results obtained from physical testing and are considered reliable. Table 1 defines a set of parameters used throughout this section.

## Table 1. THERMAL ANALYSIS PARAMETERS

| Symbol              | Definition                                               |  |  |

|---------------------|----------------------------------------------------------|--|--|

| TJ                  | Junction Temperature                                     |  |  |

| T <sub>A</sub>      | Ambient Temperature                                      |  |  |

| PD                  | Power Dissipation                                        |  |  |

| $R_{\theta-JL}$     | Thermal Resistance from Junction to Location "L"         |  |  |

| R(u) <sub>EFF</sub> | Effective (maximum) Thermal Resistance of<br>Package     |  |  |

| $\Psi_{Fn-L}$       | Thermal Reference between Foot "n" and loca-<br>tion "L" |  |  |

| $\Psi_{J-L}$        | Thermal Reference between Junction and loca-<br>tion "L" |  |  |

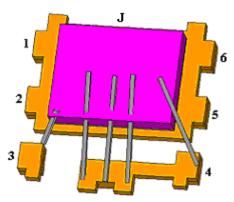

The number designation associated with "foot" in the subscript of each  $\Psi$  (read psi) term corresponds to the pin identification number as shown in Figure 7.

Figure 7. Foot and Junction Identification

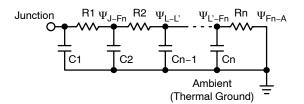

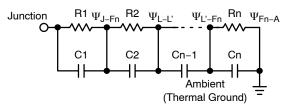

Figures 8 and 9 represent Cauer and Foster Ladders respectively. This technical note assumes the reader has a general understanding of these networks. Please refer to the documentation cited under references for detailed descriptions of thermal RC networks. In this section, the Foster network is used to calculate various thermal characteristics. For example, as seen in Figure 9, a particular thermal resistance occurs between the junction and C1/C2 node (denoted here as  $\Psi_{J-L}$ ). Then, the sum of all thermal resistances between the C1/C2 node and the Cn–1/Cn node is called a junction–to–foot thermal *reference* ( $\Psi_{J-Fn}$ ). Therefore, in the case of Figure 9, the junction–to–ambient thermal *resistance* ( $R_{\theta JA}$ ) is measured as the sum of thermal references such that,

$$\mathsf{R}_{\theta\mathsf{J}\mathsf{A}}=\Psi_{\mathsf{J}\mathsf{F}\mathsf{n}}+\Psi_{\mathsf{F}\mathsf{n}\mathsf{A}} \tag{eq. 1}$$

# Figure 8. Grounded Capacitor Thermal Network ("Cauer" Ladder)

Figure 9. Non–Grounded Capacitor Thermal Network ("Foster" Ladder)

## Junction-to-Foot/Foot-to-Ambient

The Foster Network junction-to-foot thermal references and foot-to-ambient thermal references under steady state conditions are outlined in Table 2.

## Table 2. THERMAL REFERENCE PARAMETERS

| 10% Duty                | Junction-to-Foot        |                              |  |

|-------------------------|-------------------------|------------------------------|--|

| Cycle                   | Min-Pad Size            | 1 in sq. Pad                 |  |

| PD                      | 0.7 W                   | 1.9 W                        |  |

| Copper Area             | 30 mm² (2 oz)           | 1.127 in <sup>2</sup> (2 oz) |  |

| $\Psi_{JF2}$            | 13.9°C/W                | 15.2°C/W                     |  |

| $\Psi_{JF3}$            | 51.1°C/W                | 26.3°C/W                     |  |

|                         |                         |                              |  |

| 10% Duty                | Foot-to-                | -Ambient                     |  |

| 10% Duty<br>Cycle       | Foot-to<br>Min-Pad Size | -Ambient<br>1 in sq. Pad     |  |

|                         |                         |                              |  |

| Cycle                   | Min-Pad Size            | 1 in sq. Pad                 |  |

| Cycle<br>P <sub>D</sub> | Min-Pad Size            | 1 in sq. Pad<br>1.9 W        |  |

A relationship for the thermal resistance  $(R_{\theta-JnA})$  of each device is established by using either of the following relationships,

$$\mathsf{R}_{\theta\mathsf{J}\mathsf{A}} = \Psi_{\mathsf{J}\mathsf{F}2} + \Psi_{\mathsf{F}2\mathsf{A}} \tag{eq. 2}$$

$$\mathsf{R}_{\theta\mathsf{J}\mathsf{A}} = \Psi_{\mathsf{J}\mathsf{F3}} + \Psi_{\mathsf{F3}\mathsf{A}} \tag{eq. 3}$$

Substituting appropriate values, from Table 2, into the above equations yields  $R_{\theta JA} = 69.7^{\circ}C/W$  for the one-inch square pad size and  $R_{\theta JA} = 186.3^{\circ}C/W$  for min pad size.

### Junction-to-Ambient

Table 3 outlines the junction-to-ambient thermal analysis of the WDFN6 506AP package surface mounted on an FR4 board. Substituting values from Table 3 into Equation 4 allows various junction temperatures to be calculated at assumed ambient temperatures.

$$T_J = R_{\theta JA} \times P_D + T_A$$

(eq. 4)

The effective thermal resistance of the package,  $R(u)_{EFF}$ , is defined as a function of DC or transient response. These two cases are modeled by Equations 5 and 6 respectively.

$$R(DC)_{EFF} = \frac{(T_{J} - T_{A})}{P_{D}}$$

(eq. 5)

$$R(t)_{EFF} = \frac{\left(T_{J(Pulse)} - T_{A}\right)}{P_{D}} \qquad (eq. \ 6)$$

#### Table 3. JUNCTION-TO-AMBIENT THERMAL CHARACTERISTICS

|                               | Steady State                 |                                       | Pulsed Time = 5 seconds      |

|-------------------------------|------------------------------|---------------------------------------|------------------------------|

| 10% Duty Cycle                | 1 in sq. Pad                 | Min-Pad Size                          | 1 in sq. Pad                 |

| Copper area                   | 1.127 in <sup>2</sup> [2 oz] | 30 mm <sup>2</sup> [2 oz]             | 1.127 in <sup>2</sup> (2 oz) |

| T <sub>A</sub>                | 25.0°C                       | 25.0°C                                | 25.0°C                       |

| PD                            | 1.90 W                       | 0.70 W                                | 1.90 W                       |

| $R_{	ext{	heta}JA}$           |                              |                                       | 69.7°C/W*                    |

| R <sub>(DC)EFF</sub>          | 00 700 444                   |                                       |                              |

| R(singlepulse) <sub>EFF</sub> | 69.7°C/W                     | 186.3°C/W                             | 38.2°C/W*                    |

| R(pulsed) <sub>EFF</sub>      |                              | l l l l l l l l l l l l l l l l l l l | 41.3°C/W                     |

| TJ                            |                              |                                       | 157.4°C                      |

| T <sub>J</sub> (single pulse) | 157.4°C                      | 155.4°C                               | 97.5°C*                      |

| T <sub>.1</sub> (pulsed)      |                              |                                       | 103.5°C*                     |

\*Refer to Appendix-A for R(t) Derivation

#### Junction-to-Board

Table 4 outlines the junction-to-board thermal analysis of the WDFN6 506AP package surface mounted on an FR4 board. Substituting values from Tables 2 and 4 into Equation 7 allows various junction temperatures to be calculated at assumed board temperatures.

$$\mathsf{T}_{\mathsf{J}} = \mathsf{P}_{\mathsf{D}} \times \left(\mathsf{R}_{\mathsf{\theta}\mathsf{J}\mathsf{A}} - \Psi_{\mathsf{F}\mathsf{2}\mathsf{A}}\right) + \mathsf{T}_{\mathsf{BOARD}} \tag{eq. 7}$$

#### Table 4. JUNCTION-TO-BOARD THERMAL CHARACTERISTICS

|                                | Steady                       | Steady State  |                              |

|--------------------------------|------------------------------|---------------|------------------------------|

| 10% Duty Cycle                 | 1 in sq. Pad                 | Min–Pad Size  | 1 in sq. Pad                 |

| Cu area                        | 1.127 in <sup>2</sup> [2 oz] | 30 mm² [2 oz] | 1.127 in <sup>2</sup> [2 oz] |

| PD                             | 1.90 W                       | 0.70 W        | 1.90 W                       |

| T <sub>A</sub>                 | 25.0°C                       | 25.0°C        | 25.0°C                       |

| T <sub>BOARD</sub> (DC)        |                              |               |                              |

| T <sub>BOARD</sub> (single)    | 128.5°C                      |               | 128.5°C                      |

| T <sub>BOARD</sub> (pulsed)    |                              |               |                              |

| T <sub>J (DC)</sub>            |                              |               | 157.4°C                      |

| T <sub>J</sub> (single pulse)  | 157.4°C                      | 155.4°C       | 97.5°C                       |

| T <sub>J</sub> (pulsed)        |                              |               | 103.5°C                      |

| R <sub>θ-A</sub> (DC)          |                              |               | 69.7°C/W                     |

| $R_{\theta JA}$ (single pulse) | 69.7°C/W                     | 186.3°C/W     | 38.2°C/W                     |

| $R_{\theta JA}$ (pulsed)       |                              |               | 41.3°C/W                     |

\*Refer to Appendix–A for R(t) Derivation

#### SUMMARY

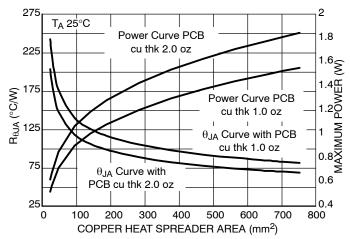

Figure 10 illustrates a steady state plot of the change in thermal resistance and max power dissipation that occurs with a change in the amount of copper spread across a given area. Evaluating the plots at the minimum recommended pad size and one–inch square pad size yields the following maximum values:

| 10% Duty Cycle    | Min-Pad Size              |                           | 1 in                         | sq. Pad                      |

|-------------------|---------------------------|---------------------------|------------------------------|------------------------------|

| Cu area (Cu thk)  | 30 mm <sup>2</sup> (1 oz) | 30 mm <sup>2</sup> (2 oz) | 1.127 in <sup>2</sup> (1 oz) | 1.127 in <sup>2</sup> (2 oz) |

| R <sub>0J1A</sub> | 222.4°C/W                 | 186.3°C/W                 | 82.7°C/W                     | 69.7°C/W                     |

| Max Power         | 0.562 W                   | 0.671 W                   | 1.51 W                       | 1.794 W                      |

Table 5. MAXIMUM RATINGS FROM FIGURE 10

Figure 11 illustrates the packages change in effective thermal resistance with respect to pulse time. The plot reflects data sampled at a minimum recommended pad size (2 oz. Cu). Under steady state conditions the plot yields  $R(t)_{EFF} = 186.34^{\circ}C/W$ . Maintaining steady state conditions and increasing the copper area to 1.0 square inch, 2 oz Cu, will yield  $R(t)_{EFF} = 69.68^{\circ}C/W$ . These results show that this package exhibits more efficient thermal characteristics than

the aforementioned SC-88 package. Although a SC-88 package carries the same footprint dimensions as a WDFN6 506AP, the minimum recommended pad size plot evaluated under steady state conditions yields  $R(t)_{EFF} = 352.4^{\circ}C/W$ . The decreased thermal resistance of a WDFN6 506AP package is attributed to the exposed flag acting as a drain contact and heat dissipation path.

Figure 10. Self-Heating Thermal Characteristics as a Function of Copper Area on the PCB

#### References

- 1. R.P. Stout, D.T. Billings, "How to Extend a Thermal–RC–Network Model (Derived From Experimental Data) to Respond to an Arbitrarily Fast Input," *ON Semiconductor*, 2006.

- 2. R.P. Stout, "Thermal RC Ladder Networks; Packaging Technology Development," ON Semiconductor, 2006.

- 3. R.P. Stout, "General Thermal Transient RC Networks," *ON Semiconductor*, 2006.

## APPENDIX

## Junction-to-Ambient Theta(t) Derivation

Equation 8 describes the relationship used to derive a model describing temperature rise for a single pulse application (see Table 6).

$$\mathsf{R(t)}_{\theta\mathsf{JA}} = \sum_{n\ =\ 1}^{m} \Psi_n \times \left[1\ -\ \mathsf{exp}(-\ t/\tau_n)\right] \quad (\mathsf{eq. 8})$$

#### Table 6. FOSTER NETWORK

Where  $R(t)_{\theta JA}$  is the total resistance of the network,  $\Psi_n$  is the resistance node, t is the length of a single pulse in seconds and  $\tau_n$  (tau) is the characteristic time of ladder. Assuming square wave impulses, the peak junction temperature is estimated by substituting  $R(t)_{\theta JA}$  into Equation 4.

| 1" Pad ( |         | 2 oz. Cu) | Min Pa  | ad (2 oz. Cu) |

|----------|---------|-----------|---------|---------------|

| n        | R (C/W) | Tau (sec) | R (C/W) | Tau (sec)     |

| 1        | 0.068   | 1.0E-06   | 0.068   | 1.0E-06       |

| 2        | 0.148   | 1.0E-05   | 0.148   | 1.0E-05       |

| 3        | 0.466   | 1.0E-04   | 0.466   | 1.0E-04       |

| 4        | 0.347   | 2.3E-04   | 0.347   | 2.3E-04       |

| 5        | 8.42    | 0.0140    | 8.42    | 0.0140        |

| 6        | 9.92    | 0.071     | 9.92    | 0.071         |

| 7        | 6.4     | 0.340     | 6.4     | 0.340         |

| 8        | 4.0     | 4.41      | 15.4    | 0.42          |

| 9        | 7.9     | 1.67      | 64.3    | 10.98         |

| 10       | 32      | 72.4      | 80.9    | 31.3          |

#### PACKAGE DIMENSIONS

WDFN6 2x2

CASE 506AP-01 **ISSUE B** n Α В F PIN ONE REFERENCE  $\bigcirc$ 0.10 С 2X С □ 0.10 2X AЗ 0.10 C Δ ○ 0.08 С 7X A1 SEATING Plane C D2 4X е 6X L 2 3 Ti b1 6X 0.10 С А В E2  $\oplus$ С 0.05 μI NOTE 5 4 ĸ┘ 6 b 6X 0.10 С А В .1 ¢ С 0.05 NOTE 3 J1 BOTTOM VIEW

NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASUBED RETWEEN 0.15 AND 0.20mm EPOM

- IS MEASURED BETWEEN 0.15 AND 0.20mm FROM TERMINAL 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

- WELL AS THE TERMINALS. 5. CENTER TERMINAL LEAD IS OPTIONAL. TERMINAL

- LEAD IS CONNECTED TO TERMINAL LEAD # 4. 6. PINS 1, 2, 5 AND 6 ARE TIED TO THE FLAG.

|     | THE I, E, OTHE OTHE HED |      |  |  |

|-----|-------------------------|------|--|--|

|     | MILLIMETERS             |      |  |  |

| DIM | MIN                     | MAX  |  |  |

| Α   | 0.70                    | 0.80 |  |  |

| A1  | 0.00                    | 0.05 |  |  |

| A3  | 0.20 REF                |      |  |  |

| b   | 0.25                    | 0.35 |  |  |

| b1  | 0.51                    | 0.61 |  |  |

| D   | 2.00 BSC                |      |  |  |

| D2  | 1.00                    | 1.20 |  |  |

| E   | 2.00 BSC                |      |  |  |

| E2  | 1.10                    | 1.30 |  |  |

| е   | 0.65 BSC                |      |  |  |

| K   | 0.15 REF                |      |  |  |

| L   | 0.20                    | 0.30 |  |  |

| L2  | 0.20                    | 0.30 |  |  |

| J   | 0.27 REF                |      |  |  |

| J1  | 0.65 REF                |      |  |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

μCool is a trademark of Semiconductor Components Industries, LLC (SCILLC).

ON Semiconductor and IIII are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative